ITER Prototype Fast Plant System Controller

Project Leader: Bruno Soares Gonçalves

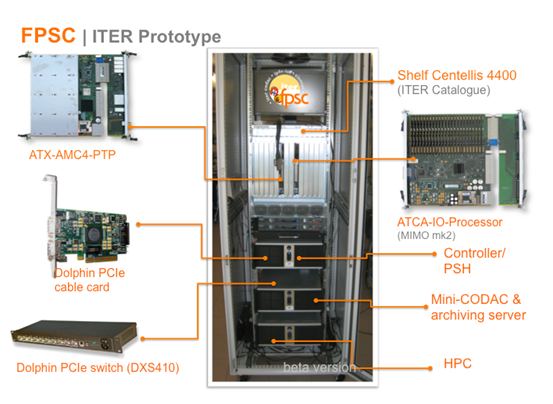

ITER Fast Plant System Controllers (FPSC) are based on embedded technologies and will be devoted to both data acquisition tasks (sampling rates > 1 kSPS) and control purposes in closed-control loops whose cycle times are below 1 ms. Fast Controllers will be dedicated industrial controllers with the ability to: i) supervise other fast and/or slow controllers; ii) interface to actuators and sensors and high performance network. This project aimed at the development of ITER prototype FPSC, specialized for data acquisition.

Two prototype systems were developed: i) based on the Advanced Telecommunications Computing Architecture (ATCA) standard under the responsibility of IST; and ii) based on PXIe under the responsibility of CIEMAT. This prototyping activity contributes to the ITER Plant Control Design Handbook (PCDH) effort of standardization, specifically regarding fast controller characteristics.

Instituto Superior Técnico (IST), from Portugal lead the consortium which also includes Centro de Investigaciones Energéticas, Medioambientales y Tecnológicas (CIEMAT), from Spain and Universidade Politecnica de Madrid (UPM).

The contract had a duration of 2 years and a total budget of 1.5M€. This was the first contract awarded to IPFN directly from ITER. Since 2009 IST has had several contracts related to ITER construction for the development of remote handling systems, participates in the consosrtium that provides Provision of System & Instrumentation Engineering support to F4E, participates on the consortium for the development of the ITER neutron cameras (contributing to the development of the data acquisition system) and has recently been awarded a contract with the value of 8.5M€ for the development of the ITER Plasma Position Reflectometry Diagnostic Systems.

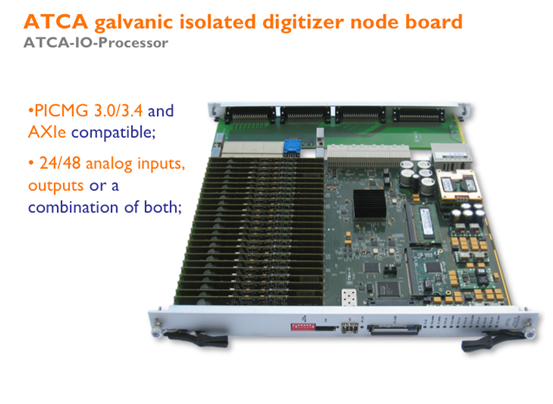

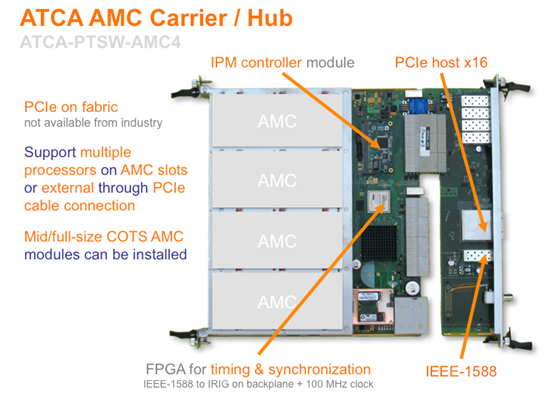

For the IST prototype, a new family of ATCA modules was developed, targeting ITER requirements. The modules comprise an AMC carrier/data hub/timing hub compliant with the upcoming ATCA extensions for Physics and a multi-channel with galvanic isolation hot-swappable digitizer designed for serviceability. The design and test of a peer-to-peer communications layer for the implementation of a reflective memory over PCI Express and the design and test of an IEEE-1588-2008 transport layer over a high performance serial link was also performed. The project brought together the work of 10 engineers per year.